距离摩尔定律的极限越来越近,行业已经走到隧道的尽头,半导体技术将变得更加难以发展,2纳米将会是芯片巨头抢滩的关键一战。

今年1月,荷兰ASML生产的第一台High-NA EUV光刻机首次开箱面世。这台总重约150吨、需250个集装箱才能装下的庞然巨物,可将世界上最先进的芯片制程从3纳米进一步缩小至2纳米。它的出现也打响了半导体厂商量产2纳米芯片的第一枪。

作为全球排名第一的晶圆代工厂,台积电是跑得最快的选手。

据台湾《工商时报》3月29日报道,台积电2纳米制程布局全线提速,公司位于新竹宝山Fab20 P1厂将于4月进行设备安装工程,为其2纳米芯片量产热身准备,预计台积电宝山P1、P2及高雄三座先进制程晶圆厂均于2025年量产,吸引苹果、英伟达、AMD及高通等客户争抢产能。

虽然台积电回复媒体称不发表评论,但按照公司2022年7月在投资者会议上公布的路线图,2纳米制程将在2024年试产,2025年量产。台积电正按规划时间表如期于今年开启2纳米芯片的生产。

除台积电外,2纳米赛道上也出现了三星、英特尔追赶的身影。

2纳米变成新战场

按照半导体行业经典的摩尔定律,集成电路可容纳的晶体管数目,每隔18个月便会增加一倍,性能相应也增加一倍。大众所知的几纳米通常指代晶体管的尺寸,为在集成电路上尽可能容纳更多的晶体管,从10纳米到7纳米,再到5纳米、3纳米,晶体管尺寸越做越小,芯片也相应越来越小。

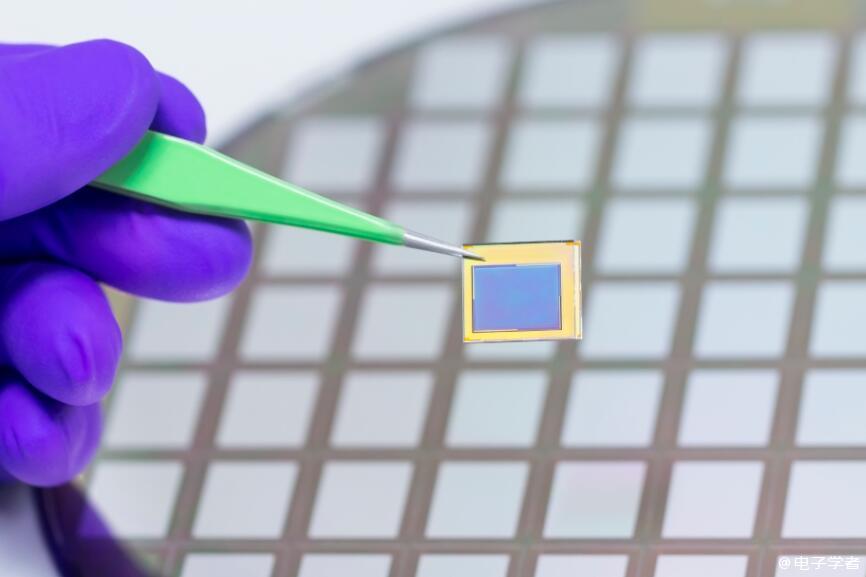

2纳米最早出现在2021年。IBM当时发布了全球首颗2纳米制程的芯片。根据官方资料介绍,IBM的这颗2纳米制程芯片是将大约500亿晶体管放在一片指甲盖大小的芯片上,与7纳米制程的芯片相比,其运算速度将快45%,效率则将提高75%。但业内普遍认为IBM作为研究机构,尚不具备量产的能力,2纳米制程芯片从实验室到量产,还需要一段时间。

在芯片制程尺寸不断缩小的过程中,芯片厂商需要解决的问题更多,例如漏电。在台积电为2纳米芯片设计的技术方案中,首次用上了GAAFET架构。GAAFET架构全称全包围栅场效应晶体管,与突破14纳米制程以下沿用的FinFET架构不同,GAAFET利用栅电极覆盖电流通道的四个侧面,而非传统的三个,能够让晶体管继续缩小下去而不漏电,从而允许在降低运行功率的情况下显着提高性能。

类似具有里程碑意义的方案还包括晶圆背面供电。较于传统正面供电,这项技术能够降低电压降,从而减少功耗,显著提升芯片性能的表现。

此前,三星已经在其3纳米制程上采用了上述两项技术方案,英特尔也在持续跟进。多位产业人士表示,从2纳米开始,GAAFET与背部供电将会成为行业标配。

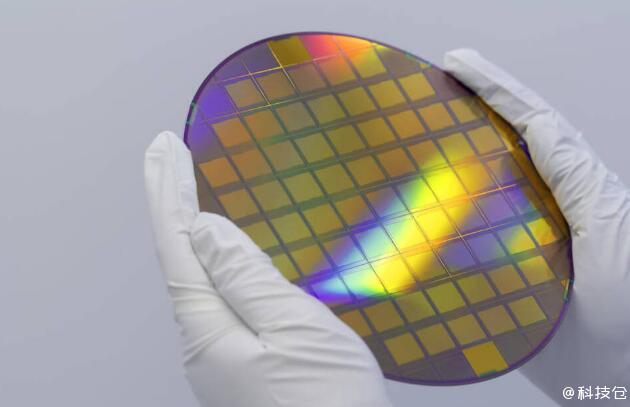

长期关注半导体制程工艺的全德学投资总监方亮向界面新闻介绍,每一代制程在内部大致分研发与量产两个阶段。芯片厂首先在实验室不计代价地投入制造出少量的晶圆,紧接着掌握技术、提升良率至30%-40%;然后量产部门就会接手,依次进行风险试产、小规模量产,再到大规模量产,不断推高良率并提升产能。等到芯片良率达到60%-70%左右,就可以基本保证“商业化阶段凑活够用”。

当一家芯片厂商在某代制程芯片上可以保持80%以上的良率,月产能攀升至10万片,它就基本能在这一代先进制程工艺上站稳脚跟。

同时,为保持足够快的迭代节奏,芯片厂商会保持“量产一代、研发一代、储备一代”的工作流程。

据《财经十一人》此前报道,台积电一般会有三个团队,同步开展三代制程的研究。一个团队从事3纳米制程的研发和良率的提升,一个团队从事2纳米制程的研发,还有一个团队会进行1.5纳米制程路径的研发。3纳米制程量产后,3纳米制程的团队就会跳到1.5纳米的团队加入研发,1.5纳米的团队就跳往下一代更小制程的路径研发,如此滚动接力。因此外界看来每两年推出一代先进制程的周期,内部布局常常有五六年之久。

按照三星、台积电、英特尔三家已经公布的时间表,2纳米将在2025年实现量产,而该年被行业视作一道分水岭。随着芯片尺寸越做越小,每一代制程的成本投入更大,性能提升的幅度反而更小。

摩尔定律的提出者、已故的英特尔创始人戈登·摩尔曾预测摩尔定律的极限将于2025年左右到来,台积电创始人张忠谋也持有同一观点。

2nm晶圆厂最快年内建成?

当前3nm工艺为业内最先进的制程技术,与此同时台积电、三星、英特尔、Rapidus等厂商积极推动2nm晶圆厂建设,台积电、三星此前曾规划2nm芯片将于2025年量产,Rapidus则计划2nm芯片将于2025年开始试产。

随着这一时间逐渐临近,全球2nm晶圆厂建设加速进行中。

近期,国际半导体产业协会(SEMI)对外表示,预计台积电与英特尔两家大厂有望今年年底之前建成2nm晶圆厂。

其中英特尔有望率先实现2nm芯片商用,英特尔PC CPU Arrow Lake产品将采用2nm制程工艺节点,台积电2nm工艺将有望应用于苹果iPhone AP芯片中,后续台积电2nm产能将大幅上升。

另据台媒报道,台积电2nm制程设备安装加速,台积电新竹宝山Fab20 P1厂计划于今年4月进行设备安装工程,有望于下半年开始试产,2025年二季度小量生产。

英特尔方面,去年年底ASML已将全球首台高数值孔径 High NA EUV EXE:5200交付给了英特尔,助力后者生产2nm芯片。随后英特尔开启了光刻机调试工作,并且进展顺利。

今年2月英特尔和ASML技术支持团队联合宣布已打开EXE:5000光刻机的光源,并使光线到达抗蚀剂。业界表示,这是光刻机正式投入使用前的一项重要准备工作,代表光刻机的光源已经正常工作了。此后,英特尔又对外分享视频,展示了首台High-NA EUV 光刻机交付过程,相关组件通过空运从荷兰运到美国,相比海运进一步缩短了交货时间。

ASML才是最大赢家

英特尔已经拿到了ASML最新的2nm芯片EUV光刻机。这种EUV光刻机型号叫做EXE:5200,和之前的EUV光刻机相比,最大变化是数值孔径NA,从低数值0.33,变成了现在的0.55。外界称这种新的EUV光刻机是High-NA系统,之前的称之为Low-NA系统。

ASML之前就表示过,当NA提升到0.55之后, 基本无法现提升了,所以ASML认为这种光刻机,可能是最后一代EUV光刻机,未来能不能提升,ASML自己也没有信心了。

这种光刻机,能够用于2nm及以下芯片的制造,因为NA更高,分辨率就更高,工艺制程就能更低,据称最低可以实现到1nm以下芯片的制造。这种NA=0.55的光刻机,重150吨(15万公斤),运输的时候,需要250个集装箱盒子,同时在拆开运到目的地之后,需要250个工人,安装调试6个月(180天)之久,才能够全部安装完成。

目前台积电、三星两家已经实现了3nm工艺,按照规划,这两家晶圆厂,将会在2025年实现2nm,而intel则表示将在2024年实现2nm工艺。

所以不用怀疑,这种新一代的EUV光刻机,一定会再次遭到几大晶圆厂的疯抢,因为大家都想在2nm时候,占据先机,抢夺更多的产能,成为晶圆制造的老大。

所以近日,ASML表示称,自己已经收到几大客户关于新EUV光刻机的订单,数量大约是20个左右。而未来它要争取能够每年生产20个这样的光刻系统。而这种光刻机,一台价格大约在3.8亿美元,20台就是76亿美元,算下来就是540亿元人民币。而上一代EUV光刻机的价格只有1.8亿美元左右。

和上一代光刻机相比,每台高出2亿美元,20台就是40亿美元,相当于290亿元,ASML真的是大赚特赚了,因为新一代的成本,肯定不会提升100%吧。